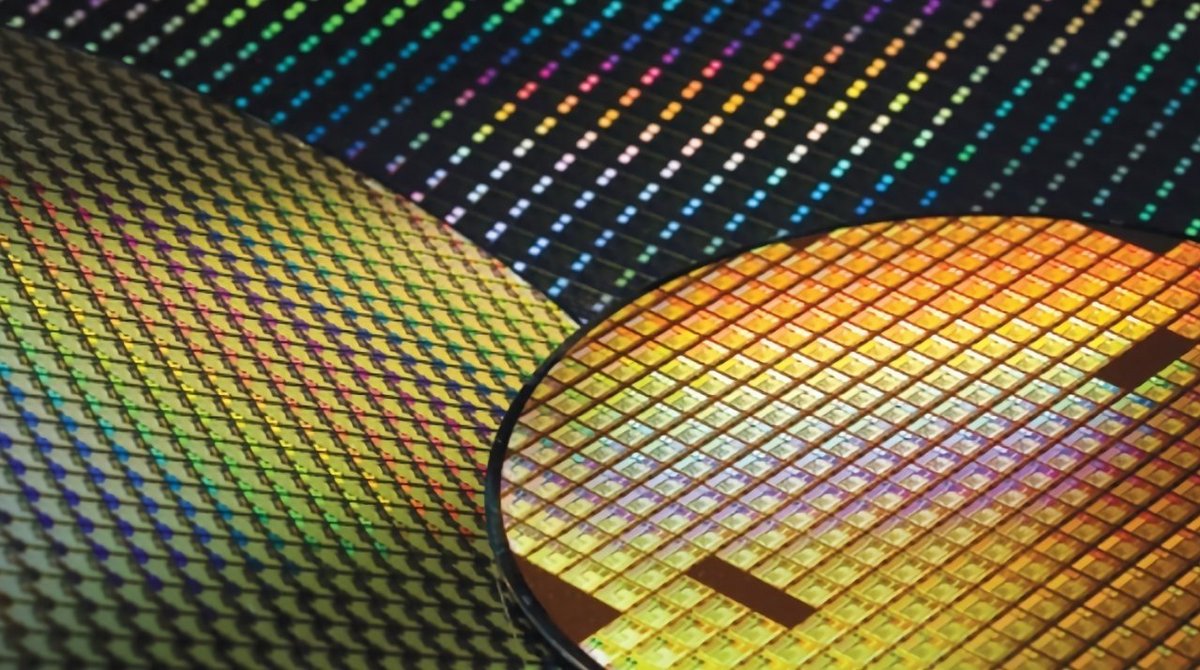

Les procédés de gravure les plus modernes ne concernent plus que trois entreprises : Intel, Samsung et TSMC.

Ces derniers mois, Intel s'est accaparé une large part de la communication autour des procédés de gravure de semi-conducteurs. La firme américaine a effectivement dans l'idée de revenir dans la course.

Mais, bien sûr, TSMC – l'actuel numéro un du semi-conducteur – n'entend évidemment pas se laisser rattraper sans réagir. La dernière feuille de route du groupe taïwanais se montre particulièrement ambitieuse.

Gravure en 1 nm en 2030

Organisée il y a une quinzaine de jours à San Francisco, l'IEDM (International Electron Devices Meeting) a été l'occasion pour les principaux acteurs de mettre en avant certaines de leurs avancées.

Pour TSMC, il s'agissait surtout de mettre les points sur les « i » et souligner combien l'avenir de la société taïwanaise est radieux avec une feuille de route très ambitieuse qui devrait permettre de garder à distance ses principales concurrentes que sont l'Américaine Intel et la Sud-coréenne Samsung.

Cette feuille de route n'est évidemment pas à prendre pour argent comptant dans la mesure où TSMC peut aussi bien prendre de l'avance que du retard sur ce qui n'est donc qu'une sorte de calendrier prévisionnel pour atteindre, courant-2030, le procédé de gravure A10.

Plus de mille milliards de transistors !

Un procédé qui fera logiquement suite au A14 lequel doit déjà faire évoluer le N2/N2P à l'horizon 2027. Alors que le N2 est gravé en 2 nm, il est logiquement question de gravure 1,4 nm pour l'A14 et de gravure 1 nm pour l'A10.

Une telle finesse ne sera évidemment pas sans poser d'incroyables défis techniques, mais si TSMC est en mesure de les relever, elle devrait battre des records de densité de transistors. À l'heure actuelle, l'un des processeurs monolithiques les plus complexes est le GH100 de NVIDIA avec ses 80 milliards de transistors, mais TSMC envisage donc d'aller beaucoup plus loin.

En effet, grâce au procédé A10, il serait possible de dépasser les 200 milliards de transistors sur une puce monolithique à l'horizon 2030. Bien sûr, il n'est pas question de ne proposer que des puces monolithiques et TSMC n'oublie pas les avancées en matière de packaging qui permettent de créer des puces multi-chip comme peuvent le faire AMD et Intel.

De telles avancées portent de nombreux noms selon leur provenance (CoWoS, InFO, SoIC, etc.) et TSMC estime que grâce à ces techniques, toujours à l'horizon 2030, il sera possible de concevoir des puces embarquant plus de mille milliards de transistors. Un chiffre qui donne le vertige.

Source : Tom's Hardware