Pour accompagner sa gamme de GPU Xe, prévue pour 2020, Intel table sur l'ambitieuse technologie Compute Express Link (CXL). À l'instar du NVLink chez Nvidia et de l'l'Infinity Fabric chez AMD, cette dernière permet d'interconnecter plusieurs accélérateurs graphiques les uns aux autres afin de les faire travailler de concert. Pour l'heure, Intel vise essentiellement le marché professionnel et celui des datas centers.

L'année dernière, parallèlement à l'arrivée de ses nouvelles GeForce RTX sur le marché, Nvidia poussait en avant le remplaçant de son fidèle SLI : le NVLink. Dotée d'une bande passante maximale nettement plus importante (160 à 300 Go/s contre 2 Go/s), cette technologie d'interconnexion permet au monde professionnel (et au monde professionnel uniquement) de combiner à la fois les CUDA Cores de deux cartes (ou plus) mais aussi leur mémoire vidéo. Les GeForce RTX, également compatibles, doivent pour leur part se contenter d'une prise en charge largement castrée du NVLink.

Le Compute Express Link, une technologie pensée pour les cartes Xe d'Intel

À l'occasion d'un événement consacré aux technologies d'interconnexion, l'Interconnect Day 2019, Intel a lui aussi mis les pieds dans le plat... en dévoilant les détails techniques de sa propre technologie : le CXL.

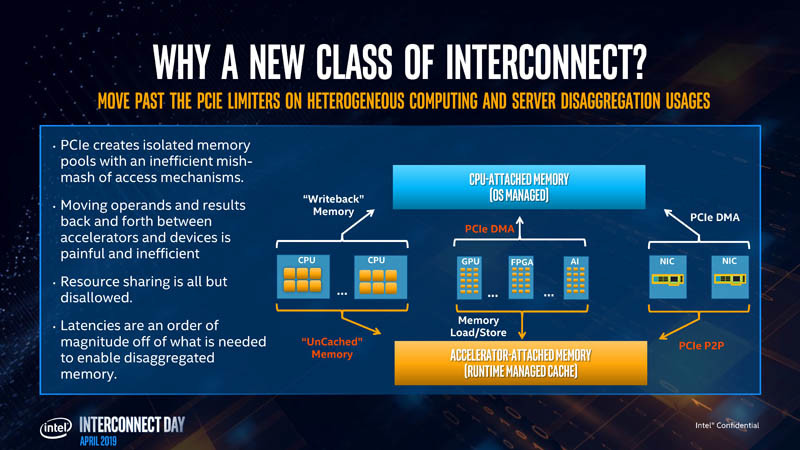

Lors de cet événement, la firme de Santa Clara a commencé par indiquer que si le PCIe reste suffisant pour le grand public, il ne peut plus convenir aux datas centers. De plus en plus demandeurs en bande passante et en mémoire partagée, ces derniers se heurtent en effet aux limitations techniques du PCI Express. Intel pointe ainsi que le PCIe isole la mémoire pour chaque appareil, s'empêtre dans des mécanismes d'accès inefficaces et rend le partage de ressources pratiquement impossible. La question de la latence, beaucoup trop élevée sur ce standard, désormais âgé, est également centrale.

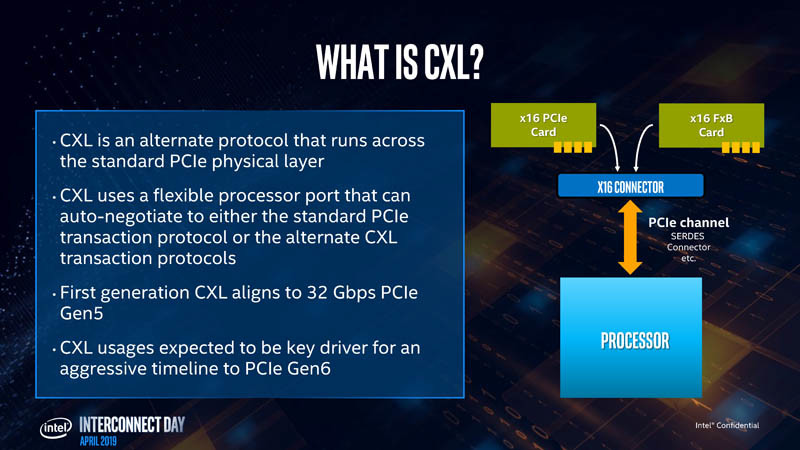

Avec le CXL, Intel veut apporter une réponse à la majorité de ces problématiques, sans pour autant compromettre ce qui fait aujourd'hui encore la force du PCIe : la simplicité et l'adaptabilité de sa couche physique, note TechPowerUp.

le CXL : une nouvelle technologie qui laissera surement sa place au futur PCI Gen 6 (PCI-SIG)

Intel a donc fait le choix de conserver la couche physique (physical layer) du PCIe pour son CXL. Sur le papier cette nouvelle technologie profite d'un maximum de 32 Gbps de bande passante par ligne et par direction, ce qui la met au niveau du PCIe Gen 5.0... La grande différence se trouve du côté de la couche de liaison (link layer), fortement remaniée par Intel.

On apprend ainsi que cette dernière profite de nouveaux protocoles d'autorégulation et de liaison. Ils viennent remplacer purement et simplement ceux du PCIe et ont été conçus dès leurs prémisses pour surmonter les difficultés qui lui étaient propres. TechPowerUp note d'ailleurs que les nouveautés apportées par le CXL pourraient à terme être plus ou moins aspirées par la norme PCIe Gen 6. De l'aveu même d'Intel, le CXL est donc une technologie transitoire. Très pertinente à l'heure actuelle, elle n'a pas pour vocation de survivre aux prochaines itérations de la norme PCIe. En clair, le CXL devrait être utilisé par Intel au moins jusqu'à l'horizon 2021-2022, le temps que le PCIe Gen 6 (PCI-SIG) soit lancé.

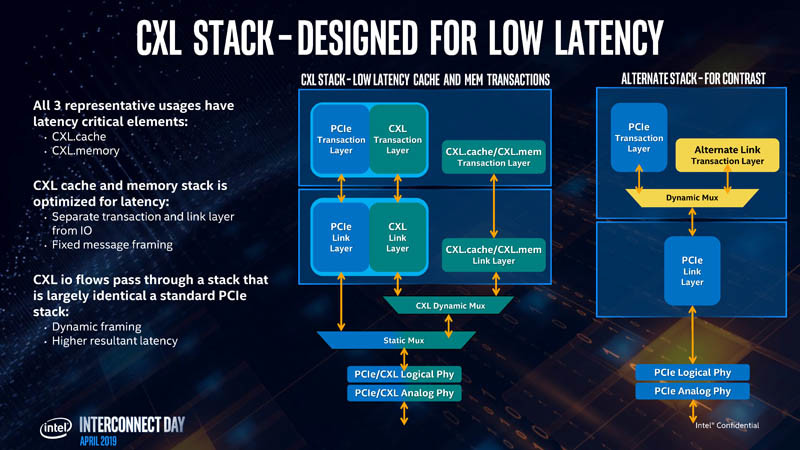

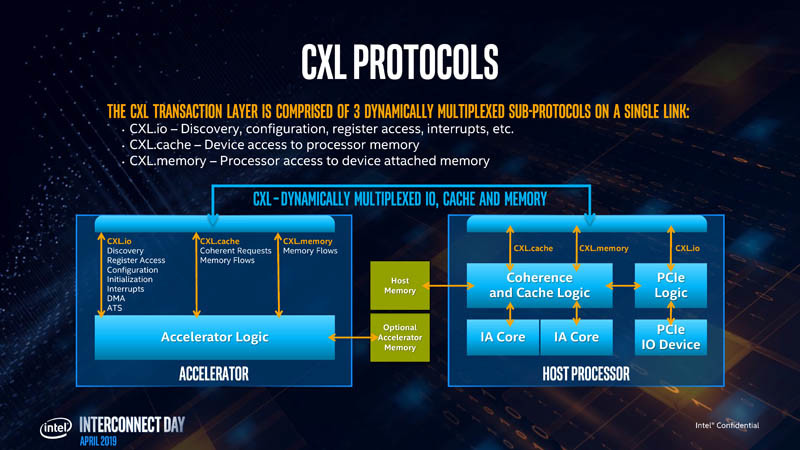

Une couche de transaction axée sur trois sous-protocoles multiplexés

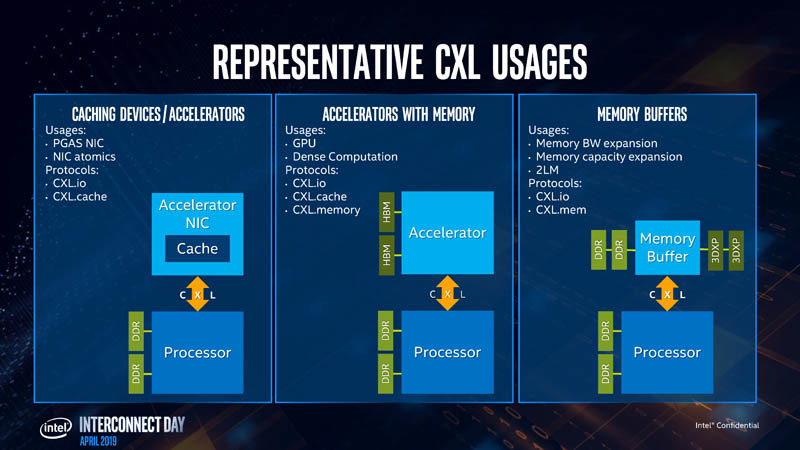

Enfin, la couche de transaction (transaction layer) se décompose pour sa part en trois sous-protocoles multiplexés, c'est à dire capables de fonctionner simultanément sur une seule ligne. Intel nomme ces trois sous-protocoles comme suit : CXL.io, CXL.cache, et CXL.memory. Ils ont chacun un rôle bien défini. Le CXL.io se charge de la découverte des appareils connectés, de la négociation des liaisons, des interruptions et des accès au registre, entre autres. Le CXL.cache s'occupe des accès à la mémoire locale, tandis que le CXL.memory se concentre sur les accès à la mémoire externe (contrôlée par un autre processeur ou une autre machine).

À la suite de sa présentation, Intel a détaillé les secteurs pour lesquels sa technologie CXL est compétente : ceux des cartes graphiques, des accélérateurs GPU ou encore des cartes de calcul haute densité. L'ensemble des trois couches de transactions du CXL sont pertinents pour ces appareils, mais les sous-protocoles CXL.io et CXL.cache sont aussi compétents pour les FPGA (Field Programmable Gate Arrays) ou encore les NIC (Network interface card, cartes réseau).

Le CXL est également très efficace dans sa gestion de la mémoire partagée. Intel assure à ce propos avoir conçu, depuis le départ, son nouveau protocole en gardant l'objectif d'une latence la plus faible possible.